本文主要阐述特定的低延迟变化的设计思想,在低成本FPGA上利用嵌入式SERDES收发器和CPRI IP(知识产权)核实现。 RRH的部署 从“Hotel”基站分离射率(RF)收发器和功率放大器的优点已经写得很多了,如图1所示。...

”基于低成本FPGA的CPRI IP核实现“ 的搜索结果

基于低成本FPGA的FFT设计实现.pdf

基于FPGA低成本动目标侦测系统的设计与实现.pdf

基于FPGA的低成本长距离高速传输系统的设计与实现.pdf

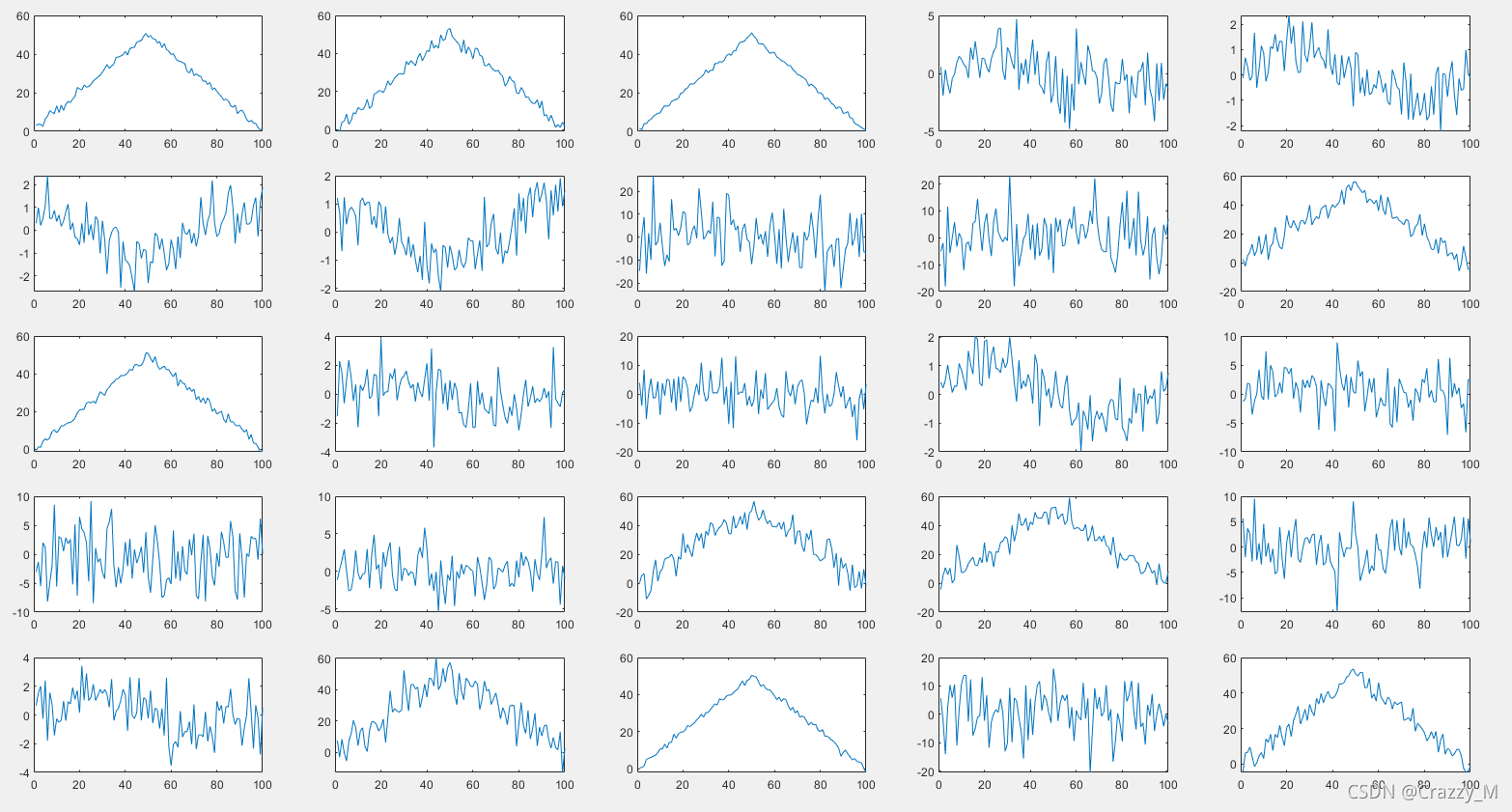

基于FPGA的FIR低通滤波器实现(附工程源码),matlab+vivado19.2+simulation

Xilinx FPGA FFT IP核完整的Vivado工程,用于实现FFT算法,可直接进行波形仿真,测试过没问题,另外还包含matlab仿真文件,时序波形仿真结果和matlab结果一致。

目录: 简介 框架 资源分配(1) 资源分配(2) 数据量化(1) 数据量化(2) 数据读写 卷积模块 池化、全连接与输出 ...事先声明,仅用于记录和讨论,有任何问题欢迎批评指正,只是觉得菜的大佬们请绕路,就不用在...

近来复旦微、国微等厂家相继推出了可以兼容XILINX...复旦微作为国内首家正向FPGA做的比XILINX还牛逼的厂家,弄出来的PCIe软核肯定也是很了不得。国微则作为反向界的扛把子,真想看看这次这个PCIe软核是否和反向有关系。

基于FPGA的低成本虚拟测量系统实现 西安电子科技大学学生的硕士论文

从新需求的角度出发,提出了一种以低成本FPGA为平台的1553B总线RT终端IP核方案,以片内逻辑实现1553B的全部RT终端协议.详细介绍了基于FPGA的1553B总线RT终端IP核硬件总体设计方案,IP核设计方法以及基于FPGA的1553B总线...

基于FPGA的FFT算法实现

标签: fpga

本系列的2-7篇分别介绍了FIR和IIR滤波器的FPGA实现。除了数字滤波器外,快速傅里叶变换(FFT)也是DSP系统常用的运算单元,用于对信号进行频域分析。FFT算法的实现很复杂,但Altera和Xilinx都提供了可快速上手使用的...

本文介绍一种基于FPGA的1维卷积神经网络算法加速实现的方案,其中为了进一步提升运算速度,除了第一层卷积采用的是普通卷积运算(CONV),其余卷积层和池化层采用的是二值化运算,即二值化的卷积与池化。 运算过程...

花了几个小时了解并写了这篇博客,不得不说的是了解的还是皮毛而已,但尽力写的详细点,这比较适合新手,老手可以忽略繁琐的部分。

基于FPGA的运动目标检测跟踪系统项目,FPGA项目,FPGA图像处理。本项目提供完整项目源程序,仿真程序,在线逻辑分析,以及讲解答疑等。2.各模块的RTL编写与仿真,在线逻辑分析,程序调试等。更多FPGA图像处理算法...

基于RGMII的以太网MAC的FPGA实现代码,整个工程采用Verilog HDL实现,包括测试用例以及功能验证TestBench

推荐文章

- 小说网站系统源码|PHP付费小说网站源码带app-程序员宅基地

- Swift编码规范_swift 正则判断文件类型-程序员宅基地

- 关于shell 中return用法解释(转)_shell return-程序员宅基地

- Linux编译宏BUILD_BUG_ON_ZERO-程序员宅基地

- c51语言单片机打铃系统设计,基于单片机的自动打铃系统的设计-程序员宅基地

- 在php中使用SMTP通过密抄批量发送邮件-程序员宅基地

- python数据清洗+数据可视化_python课程题目数据清除与可视化-程序员宅基地

- 【11g】3.3 Oracle自动存储管理存储配置_oraclestorageoptions-程序员宅基地

- signature=b2f9171fa2897cefe08a669efaf58433,FULFILLMENT TRACKING IN ASSET-DRIVEN WORKFLOW MODELING-程序员宅基地

- 宜兴市计算机中等学校,重磅!江苏省陶都中等专业学校正式揭牌!-程序员宅基地